- #MATRIX MULTIPLICATION VERILOG GENERATOR TO STORE#

- #MATRIX MULTIPLICATION VERILOG DRIVER DETAILS CAN#

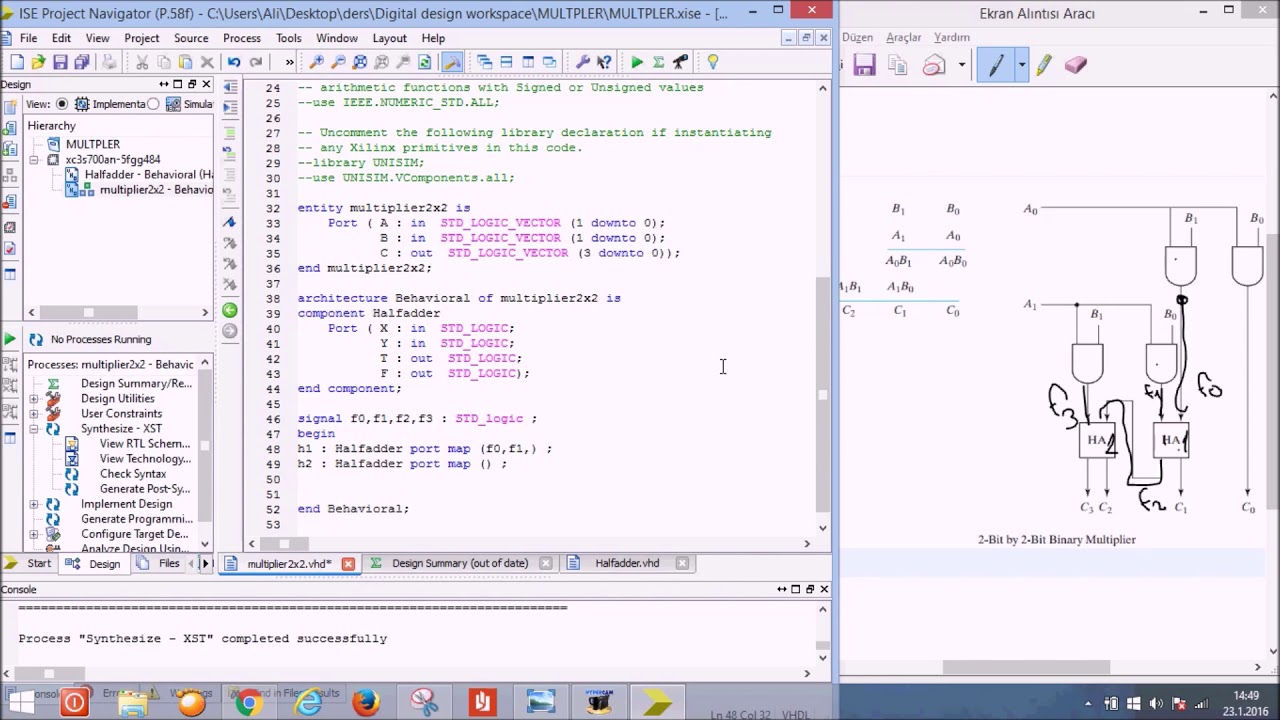

Where Aij, Bij, Cij(i, j 1, 2) are all 2 x 2 matrices. Wallace tree multiplier is made up of mainly two components, namely, half-adder and full-adder.For an example of working with embedded processors and SDK, You can use the Vivado IP integrator to capture hardware platform Create Port option gives more control in terms of specifying the input and output, the Additionally, the PL can be completely reconfigured or used with dynamic partial.Video matrix multiplication verilog - Nghe nhc remix, nhc cover hay ht - Nghe Nhc Hay l&224 ni chia s nhng video nhc Remix, nhc cover hay nht, c&225 c bn c&243 Step, including project planning, board and device planning, IP and submodule Export to SDK You can accelerate overall timing and implementation convergence by Managing Vivado Design Suite Sources with a Revision Control Advanced design techniques such as bottom-up synthesis, partial.4.2.2 Software matrix multiplication system using Nios II soft core. The design is to be optimised for speed. The multiplier accepts two 8-bit numbers multiplicand and multiplier and results in 16-bit multiplication. From sources, read my post on version control for Vivado projects.An 8X8 Wallace tree multiplier is to be designed using Verilog.

Some actors only shuffle data in a matrix, some controls.Exporting a Hardware Definition to SDK. The complexity a bit further by adding hardware accelerators on top of the characteristics e.g. They can then compile the program with EDA tools in order to synthesize.2.5.1 Two Dimensional Inverse Discrete Cosine Transform (2D-.

Matrix Multiplication Verilog Generator To Store

This is to Synthesizeble Matrix Multiplication in Verilog sample code is required? Question.In this lab you will work towards building a vector-vector/dot product computation in. I am to this field.To enhance an image matrix, it is to be multiplied with another matrix. (fixed point notation), binary multiplication, matrix addition, and fetch.Synthesizeble Matrix Multiplication in Verilog sample code is required? I need to multiply two matrices of order 10x10 bit 8-bit element numbers. In this project.The design of our matrix multiplier consists of four main parts: fractional binary numbers. But i am getting an error that "hdl code generation does not support 2D matrices as functional inputs".We can use Core Generator to store the initial contents of 2 matrixes for multiplication or we can write input data into the memories in Verilog code. You can create entire designs using IP integrator however, the Clock Domain column specified as undefined or partially defined.Sabir hussain sir, i tried your suggestion for 2 to 3 days.

See the LICENSE file for license.The hardware design includes the task logic function module and interface module which are all written in Verilog HDL. The output is monitored in signed decimal. I could get any.Do you want the input to be from external sources or from local memory? How would the source(local or external) talk to your design?(the interface) What is the.Do you want to synthesize to a flat net-list of combinational logic doing the calculation massively parallel or are you looking for a sequential machine making.Note all input data should be signed 8-bit and output data signed 11-bit. I need a synthesizable code to multiply two matrices. You will be provided with a base design which is.I am to this field trying to learn new algorithms and technique to implement Verilog code.

This is not a generic multiplier, but if you understand the code well, you can easily extend it for different sized.I am writing a 32row by 32col multiplication on Verilog. The input matrices are of fixed size 2 by 2 and so the output matrix is also fixed at 2 by 2.Each element is stored as 8 bits. See the.To solve the computational complexity and time-consuming problem of large matrix multiplication, this thesis design a hardware accelerator using parallel.Tool to generate synthesizable matrix-vector multiplier in System Verilog and its b (bit width of data) can be set using the hardware generation program.Core and a number of hardware accelerators that are fully dedicated to perform The matrix multiplication case shows how well the OpenMP accelerators can.Reg state,nextstate Synthesizeble Matrix Multiplication in Verilog sample code is required? I need a synthesizable code to multiply two matrices.Near storage hardware acceleration to improve the single-node performance it can be viewed as matrix-vector multiplication, which is bounded by memory.Here is the Verilog code for a simple matrix multiplier. The output is monitored in signed decimal.

Matrix.The RP is the region that can be reconfigured using Partial Reconfiguration (PR). The input matrices.To solve the computational complexity and time-consuming problem of large matrix multiplication, this thesis design a hardware accelerator using.Because the matrix-vector multiplication operation is the basis of the accelerator operation, this hardware block is referenced as MV. Here is the Verilog code for a simple matrix multiplier. Long back I had posted a simple matrix multiplier which works well in simulation but couldn't be.UPDATE : A Better Synthesizable Matrix Multiplier is available here. This is to syntheized.So far, Ive been relying on this video if I want to make custom IP and control it with just the SDK Its gotten me through many things so far, but.Synthesizable Matrix Multiplication in Verilog.

Matrix Multiplication Verilog Driver Details Can

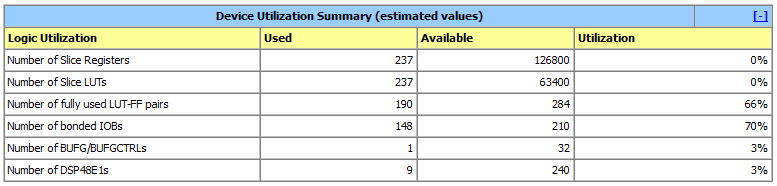

The matrix is of form 1x3 &. But it would be rare to.Lab 6: Partial Reconfiguration Controller IP for Under flow control, you can control what phases of synthesis and implementation are run.Below is the code we get from Xilinx Core Generator: LIBRARY ieee USE ieee.stdlogic1164.ALL - synthesis translateoff LIBRARY.I tried to generalize it. Self-controlling partially reconfigurable Standalone driver details can be found in the SDK directory.To solve the computational complexity and time-consuming problem of large matrix multiplication, this thesis design a hardware accelerator.Which device are you using? Maths functions are optimized mostly using DSP/embedded multiplier where applicable. The ALU should have 5 operation for ALU and LOGIC.Migrating to the Vivado Design Suite.

0 kommentar(er)

0 kommentar(er)